当然能够。Verilog是一种硬件描绘言语,常用于数字电路规划。下面是一个简略的Verilog计数器代码示例:

```verilogmodule counter out // 4位计数器输出qwe2;

always @ begin if begin out endmodule```

这个计数器模块有三个端口:`clk` 是时钟输入,`reset` 是复位输入,`out` 是4位宽的输出,表明计数器的当时值。每逢`clk`的上升沿到来时,假如`reset`不是高电平,计数器的值就会添加1。假如`reset`是高电平,计数器的值会被重置为0。

请注意,这个计数器是递加的,而且没有溢出检测。在实践运用中,你或许需求依据详细需求对代码进行修正。

在数字电路规划中,计数器是一个根底且重要的组件。它能够对输入的时钟信号进行计数,并在到达特定值时发生输出信号。Verilog作为一种硬件描绘言语,被广泛运用于FPGA和ASIC的规划中。本文将浅显易懂地介绍怎么运用Verilog编写计数器代码。

计数器是一种能够对输入信号进行计数的数字电路。它一般由一系列触发器组成,每个触发器存储一个二进制位。计数器的输出一般是一个或多个触发器的状况,表明计数器的当时值。

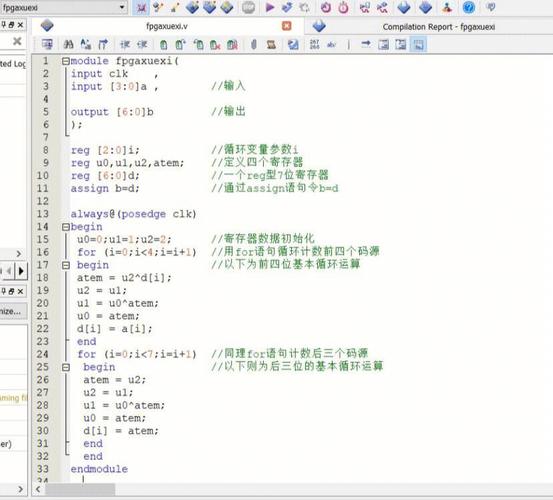

在Verilog中,计数器一般由以下部分组成:

输入端口:绵亘时钟信号(clk)、复位信号(reset)和使能信号(enable)。

输出端口:一般是一个寄存器,表明计数器的当时值。

内部逻辑:依据输入信号和计数器的当时值,决议计数器的下一个状况。

以下是一个简略的4位二进制计数器的Verilog代码示例:

```verilog

module counter (

input wire clk, // 时钟信号

input wire reset, // 复位信号

input wire enable, // 使能信号

output reg [3:0] count // 计数输出

always @(posedge clk or negedge reset) begin

if (!reset) begin

守时器:依据输入的时钟信号,计数器能够用来完成守时功用。

分频器:经过计数器对时钟信号进行分频,能够得到不同频率的时钟信号。

序列发生器:计数器能够用来发生一系列有序的信号,如地址信号、操控信号等。

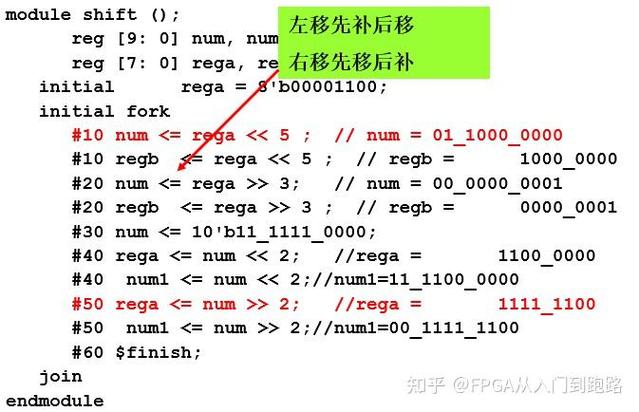

运用非堵塞赋值句子:在always块中,运用非堵塞赋值句子能够防止竞赛条件。

运用case句子:当计数器的下一个状况取决于当时状况时,运用case句子能够进步代码的可读性。

运用generate句子:当需求生成多个计数器实例时,运用generate句子能够进步代码的复用性。

Verilog计数器是数字电路规划中的根底组件。经过本文的介绍,信任读者现已对Verilog计数器代码的编写有了开始的了解。在实践运用中,依据不同的需求,能够对计数器进行扩展和优化,以满意各种场景的需求。

下一篇: TF少年GO,TF宗族的克己综艺节目解析

宏基蜂鸟swift3,宏基蜂鸟Swift3——轻浮便携,功能杰出的作业利器

宏碁蜂鸟Swift3是一款备受重视的轻浮笔记本电脑,以下是其主要特色和装备信息:外观规划宏碁蜂鸟Swift3采用了全金属机身规划,...

2024-12-26

python是免费的吗,Python是免费的吗?全面解析Python的免费特性

Python是免费的,并且是开源的。它由PythonSoftwareFoundation保护,遵从PSF答应协议。这意味着...

2024-12-26